# SDC-14610/15 Series Three Channel 14- and 16-Bit **Tracking S/D Converters**

#### **DESCRIPTION**

The SDC-14610/15 Series are small low cost three channel synchroor resolver-to-digital converters. The SDC-14610 Series is fixed at 14 bits, the SDC-14615 at 16 bits. The three channels are independent tracking types but share digital output pins and a common reference.

The SDC-14610/15 "S" option offers synthesized reference circuitry to correct for phase shifts between the reference and the signal voltage.

The velocity output (VEL) from the SDC-14610/15 Series, which can be used to replace a tachometer, is a 4 V signal referenced to ground with a linearity of 1% of output voltage.

A BIT output is optional and is a logic line that indicates LOS (Loss Of Signal) or excessive converter error and LOR (Loss Of Reference - option "S" only). Due to pin limitations this option will exclude the velocity output. (See option "T".)

SDC-14610/15 Series converters are available with operating temperature ranges of 0°C to +70°C and -55°C to +125°C, and MIL-PRF-38534 processing is available.

## **APPLICATIONS**

With its low cost, small size, high accuracy, and versatile performance, the SDC-14610/15 Series converters are ideal for use in modern high-performance military and industrial position control systems. Typical applications include radar antenna positioning, navigation and fire control systems, motor control, and robotics.

**Data Device Corporation** 105 Wilbur Place Bohemia, New York 11716 631-567-5600 Fax: 631-567-7358 www.ddc-web.com

- Make sure the next Card you purchase

- Synthesized Reference Option

- Fixed 14- or 16-Bit Resolution

- Small Size 36-Pin DDIP Package

- Three Independent Converters

- Low Cost per Channel

**FEATURES**

- Velocity Output Eliminates **Tachometer**

- Optional BIT Output (LOS and LOR)

- High Reliability Single Chip Monolithic

- -55°C to +125°C Operating Temperature Range

- MIL-PRF-38534 Processing Available

FOR MORE INFORMATION CONTACT:

**Technical Support:** 1-800-DDC-5757 ext. 7382

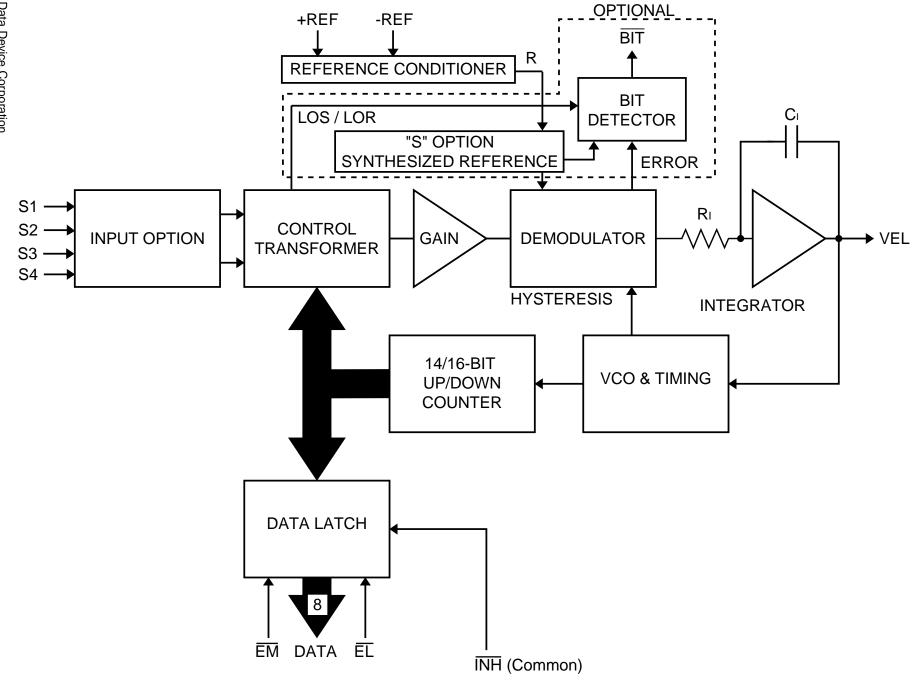

FIGURE 1. SDC-14610/15 BLOCK DIAGRAM (ONE CHANNEL)

# **TABLE 1. SDC-14610/15 SPECIFICATIONS**

These specs apply over the rated power supply, temperature, and reference frequency ranges; 10% signal amplitude variation, and 10% harmonic distortion.

| (Values are for each channel unless stated otherwise.)  |              |                                                         |          |                           |  |  |  |

|---------------------------------------------------------|--------------|---------------------------------------------------------|----------|---------------------------|--|--|--|

| PARAMETER                                               | UNIT         | VALUE                                                   |          |                           |  |  |  |

| RESOLUTION                                              | Bits         | 14                                                      |          | 16                        |  |  |  |

| ACCURACY                                                | Min          | 4 +1 LSB                                                |          | +1 LSB<br>_SB ("S" only*) |  |  |  |

| REPEATABILITY                                           | LSB          | 1 max                                                   |          |                           |  |  |  |

| DIFFERENTIAL LINEARITY                                  | LSB          | 1 max                                                   |          |                           |  |  |  |

| Type                                                    |              | (+REF, -REF),<br>COMMON TO ALL CHANNELS<br>DIFFERENTIAL |          |                           |  |  |  |

| Valla na Danna                                          | \ /          |                                                         |          |                           |  |  |  |

| Voltage Range<br>Frequency                              | Vrms<br>Hz   | 2-35<br>360-5000                                        |          | 10-130<br>see note **     |  |  |  |

| Input Impedance                                         |              | 000 0000                                                |          | 1000 11010                |  |  |  |

| single ended                                            | Ohm          | 60k                                                     |          | 270k min                  |  |  |  |

| differential Common Mode Range                          | Ohm<br>Vpeak | 120k<br>50 100 trans                                    | sient    | 540k min<br>200,          |  |  |  |

| Common wode range                                       | VPCCIK       | 50,100 transient                                        |          | 300 transient             |  |  |  |

| Option "S"                                              | l , ,        | 0.05                                                    |          |                           |  |  |  |

| Voltage Range<br>Frequency                              | Vrms<br>Hz   | 2-35<br>1k-5k                                           |          |                           |  |  |  |

| Input Impedance                                         | 112          | TK OK                                                   |          | _                         |  |  |  |

| single ended                                            | Ohm          | 40k                                                     |          | _                         |  |  |  |

| differential Common Mode Range                          | Ohm<br>Vpeak | 80k<br>50,100 trans                                     | oiont    | _                         |  |  |  |

| ±Sig/Ref Phase Shift                                    | deg.         | 45 max                                                  | sierii   | _                         |  |  |  |

| SIGNAL INPUT                                            |              | EACH CHANNEL                                            |          |                           |  |  |  |

| CHARACTERISTICS                                         |              |                                                         |          |                           |  |  |  |

| 90 V Synchro Input (L-L) Zin line-to-line               | Ohm          | (Not Availab<br>123k                                    | ole on " | S" option)                |  |  |  |

| Zin line-to-ground                                      | Ohm          | 80k                                                     |          |                           |  |  |  |

| Common Mode Voltage                                     | V            | 180 max                                                 |          |                           |  |  |  |

| 11.8 V Synchro Input (L-L)                              |              | (Not Availab                                            | ole on " | S" option)                |  |  |  |

| Zin line-to-line                                        | Ohm          | 52k                                                     |          |                           |  |  |  |

| Zin line-to-ground Common Mode Voltage                  | Ohm<br>V     | 34k                                                     |          |                           |  |  |  |

|                                                         | V            | 30 max                                                  |          |                           |  |  |  |

| 11.8 V Resolver Input (L-L) Zin line-to-line            | Ohm          | 140k                                                    |          |                           |  |  |  |

| Zin line-to-ground                                      | Ohm          | -                                                       |          |                           |  |  |  |

| Common Mode Voltage                                     | V            | 30 max                                                  |          |                           |  |  |  |

| 2 V Direct Input (L-L)                                  |              | (Not Available on "S" option)                           |          | S" option)                |  |  |  |

| Voltage Range                                           | Vrms<br>V    | 2 nom, 2.3 max                                          |          | anaiant                   |  |  |  |

| Max Voltage No Damage Input Impedance                   | Ohm          | 25 cont, 100 pk transient<br>20 M//10 pF min            |          | ansieni                   |  |  |  |

|                                                         |              | · '                                                     |          |                           |  |  |  |

| 2 V Resolver Input (L-L) Zin single ended               | Ohm          | ("S" option only)                                       |          |                           |  |  |  |

| Zin differential                                        | Ohm          | 22k                                                     |          |                           |  |  |  |

| Common Mode Voltage                                     | V            | 4.9 max                                                 |          |                           |  |  |  |

| DIGITAL INPUT/OUTPUT Logic Type                         |              | TTL/CMOS                                                | comp     | atible                    |  |  |  |

| Inputs                                                  |              | TTL/CMOS compatible<br>Logic 0 = 0.8 V max              |          |                           |  |  |  |

|                                                         |              | Logic 1 = 2                                             |          |                           |  |  |  |

|                                                         |              | Loading (pe<br>max P.U. c                               |          | nel) =10 µa               |  |  |  |

|                                                         |              | +5 V //5 pl                                             |          | Source IO                 |  |  |  |

|                                                         |              | CMOS tra                                                |          | protected                 |  |  |  |

|                                                         |              | EACH CHA                                                | ANNEL    |                           |  |  |  |

| Inhibit (INH)(common)                                   |              | Logic 0 inhibits; Data                                  |          | ata                       |  |  |  |

| Enable Dite 4 to 0 (EM)                                 |              | stable with                                             |          |                           |  |  |  |

| Enable Bits 1 to 8 (EM)<br>Enable Bits 9 to 14(16) (EL) |              | Logic 0 enables; Data stable within 150 ns              |          |                           |  |  |  |

|                                                         |              |                                                         |          |                           |  |  |  |

| TABLE 1. SDC 1461                       | 0/15 SP                | ECIF                                                               | ICAT                | TION:      | S (C      | ONT.)          |

|-----------------------------------------|------------------------|--------------------------------------------------------------------|---------------------|------------|-----------|----------------|

| PARAMETER                               | UNIT                   |                                                                    |                     | VAL        | <u> </u>  |                |

| DIGITAL INPUT/OUTPUT                    | 0                      | Logic                                                              | 1 = F               |            |           | nce            |

| (Cont.)                                 |                        | Logic 1 = High Impedance Data High Z within 100 ns                 |                     |            |           |                |

| OUTPUTS                                 |                        | Common To All Channels                                             |                     |            |           |                |

| Parallel Data [1-14(16)]                | bits                   | 8 parallel lines; 2 bytes natural                                  |                     |            | natural   |                |

|                                         |                        | binary angle, positive logic                                       |                     |            | ogic      |                |

| Built-In-Test (BIT)                     |                        |                                                                    |                     | BIT cor    |           |                |

| (Optional)                              |                        | ±100 LSBs of error with a filter of 500 µs or LOS / (LOR-"S" only) |                     |            |           |                |

|                                         |                        | EACH CHANNEL                                                       |                     |            | ,,        |                |

| Drive Capability                        |                        | 50 pF                                                              |                     | ETL Io     | nd 16     | S m A at       |

| Drive Capability                        | TTL                    | Logic 0; 1 TTL load, 1.6 mA at 0.4 V max                           |                     |            | ) IIIA at |                |

|                                         |                        |                                                                    |                     |            | oads,     | -0.4 mA        |

|                                         |                        | at 2.8 V min<br>Logic 0; 100 mV max driving                        |                     |            | rivina    |                |

|                                         |                        |                                                                    | ,                   | V sup      |           |                |

|                                         | CMOS                   |                                                                    |                     | in driv    |           |                |

| DYNAMIC<br>CHARACTERISTICS              |                        | 60                                                                 |                     | e Type     |           | "S"<br>OPTION  |

| Each Channel                            |                        | 60 1                                                               | п∠                  | 400 HZ     |           | OI HON         |

| Input Frequency                         | Hz                     | 47-5 k                                                             |                     | 360-5 k    |           | 1 k-5 k<br>150 |

| Bandwidth(Closed Loop) Ka               | Hz<br>1/s <sup>2</sup> | 15<br>830                                                          |                     | 103<br>53k |           | 110k           |

| A1                                      | 1/s                    | 0.17                                                               |                     | 1.33       |           | 2.47           |

| A2<br>  A                               | 1/s                    | 5k                                                                 |                     | 40k        |           | 44.4k<br>333   |

| B                                       | 1/s<br>1/s             | 29<br>14.5                                                         |                     | 230<br>115 |           | 166            |

| Resolution                              | bits                   | 14                                                                 | 16                  | 14         | 16        | 16             |

| Tracking Rate typical                   | rne                    | 1.25                                                               | 0.31                | 10         | 2.5       | 2.5            |

| minimum                                 | rps<br>rps             | 1.23                                                               | 0.25                | 8          | 2.5       | 2.3            |

| Acceleration (1 LSB lag)                | deg/s <sup>2</sup>     | 18                                                                 | 4.5                 | 1160       |           | 610            |

| Settling Time (179° step max)           | msec                   | 1100                                                               | 2500                | 140        | 320       | 232            |

| VELOCITY                                |                        |                                                                    | EA                  | CH CH      | IANNI     | L<br>EL        |

| CHARACTERISTICS                         |                        |                                                                    |                     |            |           |                |

| Polarity<br>  Voltage Range(Full Scale) | ±V                     |                                                                    |                     | increa     | asing a   | angle          |

| Voltage Scaling                         | rps/FS                 | 4.5 typ, 4 min<br>10                                               |                     |            |           |                |

| Scale Factor                            | ±%                     | 10 typ 20 max                                                      |                     |            |           |                |

| Scale Factor TC Reversal Error          | ppm/°C<br>±%           | 100 typ 200 max<br>1 typ 2 max                                     |                     |            |           |                |

| Linearity                               | ±%                     | 0.5 typ 1 max                                                      |                     |            |           |                |

| Zero Offset Zero Offset TC              | mV                     | 5 typ 10 max                                                       |                     |            |           |                |

| Load                                    | μV/°C<br>kOhm          | 15 typ 30 max<br>20 max                                            |                     |            |           |                |

| Noise                                   | (Vp/V)%                | 1 typ 2 max                                                        |                     |            |           |                |

| POWER SUPPLIES                          | \                      | TOTAL DEVICE                                                       |                     |            |           |                |

| Nominal Voltage Voltage Range           | V<br>±%                | +5<br>5                                                            | - <del>(</del><br>1 | 0          |           |                |

| Max Volt. w/o Damage                    | V                      | +7 -7                                                              |                     |            |           |                |

| Current (Ea.)                           | mA                     | 36 typ, 51 max                                                     |                     |            |           |                |

| TEMPERATURE RANGE Operating             |                        |                                                                    |                     |            |           |                |

| -30X                                    | °C                     | 0 to +70                                                           |                     |            |           |                |

| -10X                                    | °C                     | -55 to +125<br>-65 to +150                                         |                     |            |           |                |

| Storage PHYSICAL                        | °C                     | -65 to                                                             | +15(                | J          |           |                |

| CHARACTERISTICS                         |                        |                                                                    |                     |            |           |                |

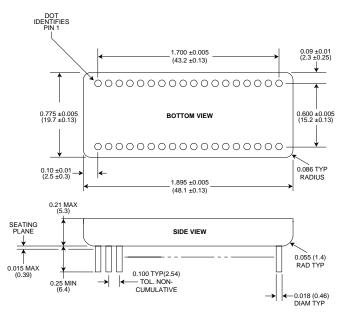

| Size                                    | in                     |                                                                    |                     | x 0.2      |           |                |

| Weight                                  | (mm)                   | (43.2<br>0.66(                                                     |                     | 8 x 5.3    | 3)        |                |

| Weight  Notes: * Applies to "S" Option  | oz(g)                  | 0.00(                                                              | 10.7)               |            |           |                |

Notes:

<sup>\*</sup> Applies to "S" Option only \*\* 47 - 5k for 90 V, 60 Hz; 360 - 5k for 90 V, 400 Hz

#### THEORY OF OPERATION

The SDC-14610/15 Series of converters are based upon a single chip CMOS custom monolithic. They are implemented using the latest IC technology which merges precision analog circuitry with digital logic to form a complete high performance tracking resolver-to-digital converter.

FIGURE 1 is the Functional Block Diagram of the SDC-14610/15 Series. The converter operates with  $\pm 5$  VDC power supplies. Analog signals are referenced to analog ground, which is at ground potential. The converter is made up of three main sections; an input front-end, a converter, and a digital interface. The converter front-end differs for synchro, resolver and direct inputs. An electronic Scott-T is used for synchro inputs, a resolver conditioner for resolver inputs and a sine and cosine voltage follower for direct inputs. These amplifiers feed the high accuracy Control Transformer (CT). Its other input is the 14-bit digital angle  $\phi$ . Its output is an analog error angle, or difference angle, between the two inputs. The CT performs the ratiometric trigonometric computation of SIN $\theta$ COS $\phi$  - COS $\theta$ SIN $\phi$  = SIN $(\theta$  -  $\phi$ ) using amplifiers, switches, logic and capacitors in precision ratios.

The converter accuracy is limited by the precision of the computing elements in the CT. In these converters, ratioed capacitors are used in the CT instead of more conventional precision ratioed resistors. Capacitors used as computing elements with op-amps need to be sampled to eliminate voltage drifting. Therefore, the circuits are sampled at a high rate to eliminate this drifting and at the same time to cancel out the op-amp offsets.

The error processing is performed using the industry standard technique for type II tracking R/D converters. The DC error is integrated yielding a velocity voltage which, in turn, drives a voltage controlled oscillator (VCO). This VCO is an incremental integrator (constant voltage input to position rate output) which, together with the velocity integrator, forms a type II servo feedback loop. A lead in the frequency response is introduced to stabilize the loop and another lag at higher frequency is introduced to reduce the gain and ripple at the carrier frequency and above.

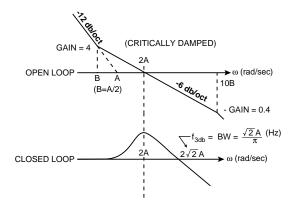

## TRANSFER FUNCTION AND BODE PLOT

The dynamic performance of the converter can be determined from its functional block diagram and its Bode plots (open and closed loop); these are shown in FIGURES 1 and 2 respectively.

The open loop transfer function is as follows:

Open Loop Transfer Function =

$$\frac{A^2 \left(\frac{S}{B} + 1\right)}{S^2 \left(\frac{S}{10B} + 1\right)}$$

where A is the gain coefficient and B is the frequency of lead compensation

The components of gain coefficient are error gradient, integrator gain, and VCO gain. These can be broken down as follows:

- Error Gradient = 0.011 volts per LSB (CT + Error Amp + Demod)

- Integrator Gain =  $\frac{1}{R_i C_i}$  volts per second per volt

- VCO Gain =  $\frac{1}{1.25 R_V C_V}$  LSBs per second per volt

#### **GENERAL SETUP CONSIDERATIONS**

The following recommendations should be considered when connecting the SDC-14610/15 Series converters:

- 1) Power supplies are  $\pm 5$  VDC. For lowest noise performance it is recommended that a 0.1  $\mu F$  or larger cap be connected from each supply to ground near the converter package.

- 2) Direct inputs are referenced to AGND.

- 3) Connect pin 5 (GND) to pin 6 (AGND) close to the hybrid.

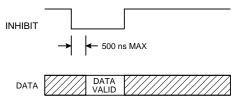

#### INHIBIT AND ENABLE TIMING

The Inhibit (INH) signal is used to freeze the digital output angle in the transparent output data latch while data is being transferred. Application of an Inhibit signal does not interfere with the continuous tracking of the converter. As shown in FIGURE 3, angular output data is valid 500 nanoseconds maximum after the application of the low-going inhibit pulse.

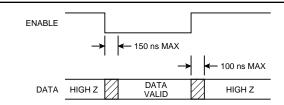

Output angle data is enabled onto the tri-state data bus in six bytes. The Enable MSB ( $\overline{EM}$ -A,  $\overline{EM}$ -B, or  $\overline{EM}$ -C) is used for the most significant 8 bits and Enable LSB ( $\overline{EL}$ -A,  $\overline{EL}$ -B, or  $\overline{EL}$ -C) is used for the least significant bits. As shown in FIGURE 4, output data is valid 150 nanoseconds maximum after the application of a low-going enable pulse. The tri-state data bus returns to the high impedance state 100 nanoseconds maximum after the rising edge of the enable signal.

**FIGURE 2. BODE PLOTS**

# BIT, BUILT-IN-TEST ("T" OPTION)

This output is a logic line that will flag an internal fault condition, or LOS (Loss-Of-Signal). The internal fault detector monitors the internal error and, when it exceeds  $\pm 100$  LSBs, will set the line to a logic 0; this condition will occur during a large-step input and will reset to a logic 1 after the converter settles out. (The error voltage is filtered with a 500  $\mu s$  filter)  $\overline{BIT}$  will set for an overvelocity condition because the converter loop can't maintain input/output sync.  $\overline{BIT}$  will also be set if a total LOS (loss of all signals) occurs or an LOR (loss of reference - "S" option only) occurs.

#### NO FALSE 180° HANGUP

This feature eliminates the "false 180° reading" during instantaneous 180° step changes; this condition most often occurs when the input is "electronically switched" from a digital-to-synchro converter. If the "MSB" (or 180° bit) is "toggled" on and off, a converter without the "false 180° reading" feature may fail to respond.

FIGURE 3. INHIBIT TIMING

|    | TABLE 2. PINOUTS (36 PIN) (SEE NOTE 1) |               |          |                                      |                                         |  |

|----|----------------------------------------|---------------|----------|--------------------------------------|-----------------------------------------|--|

| 1  | S1A(S)                                 | S1A(R)        | N.C.     | 36                                   | VEL A (Velocity Output)<br>(see Note 2) |  |

| 2  | S2A(S)                                 | S2A(R)        | +COSA(D) | 36                                   | EM-A (Enable MSBs)                      |  |

| 3  | S3A(S)                                 | S3A(R)        | +SINA(D) | 34                                   | EL-A (Enable LSBs)                      |  |

| 4  | N.C.                                   | S4A(R)        | N.C.     | 33                                   | INH (Inhibit)                           |  |

| 5  | GND (Ground)(see Note 4)               |               | 32       | VEL B (Velocity Output) (see Note 2) |                                         |  |

| 6  | AGND (Analog Ground) (see Note 4) 31   |               | 31       | EM-B (Enable MSBs)                   |                                         |  |

| 7  | S1B(S)                                 | S1B(R)        | N.C.     | 30                                   | EL-B (Enable LSBs)                      |  |

| 8  | S2B(S)                                 | S2B(R)        | +COSB(D) | 29                                   | Bit 8/Bit 16 (see Note 3)               |  |

| 9  | S3B(S)                                 | S3B(R)        | +SINB(D) | 28                                   | Bit 7/Bit 15 (see Note 3)               |  |

| 10 | N.C.                                   | S4B(R)        | N.C.     | 27                                   | Bit 6/Bit 14                            |  |

| 11 | -5 V (Power Supply)                    |               | 26       | Bit 5/Bit 13                         |                                         |  |

| 12 | +5 V (Powe                             | er Supply)    |          | 25                                   | Bit 4/Bit 12                            |  |

| 13 | S1C(S)                                 | S1C(R)        | N.C.     | 24                                   | Bit 3/Bit 11                            |  |

| 14 | S2C(S)                                 | S2C(R)        | +COSC(D) | 23                                   | Bit 2/Bit 10                            |  |

| 15 | S3C(S)                                 | S3C(R)        | +SINC(D) | 22                                   | Bit 1/Bit 9                             |  |

| 16 | N.C.                                   | S4C(R)        | N.C.     | 21                                   | VEL C (Velocity Output)<br>(see Note 2) |  |

| 17 | -REF (-Refe                            | erence Input) |          | 20                                   | EL-C (Enable LSBs)                      |  |

| 18 | +REF (+Reference Input)                |               | 19       | EM-C (Enable MSBs)                   |                                         |  |

Notes: 1. (S) = Synchro; (R) = Resolver; (D) = 2 V Resolver Direct

- 2. Replaced with BIT "T" option

- 3. SDC-14615 Series only

- 4. Connect pin 5 (GND) to pin 6 (AGND) close to the hybrid

The condition is artificial, as a "real" synchro or resolver cannot change its output 180° instantaneously. The condition is most often noticed during wraparound verification tests, simulations, or troubleshooting.

#### SYNTHESIZED REFERENCE

The synthesized reference section ("S" option) eliminates errors due to phase shift between the reference and signal inputs. Quadrature voltages in a resolver or synchro are by definition the resulting 90° fundamental signal in the nulled out error voltage (e) in the converter. Due to the inductive nature of synchros and resolvers, their output signals lead the reference input signal (RH and RL). When an uncompensated reference signal is used to demodulate the control transformer's output, quadrature voltages are not completely eliminated. As shown in FIGURE 1, the converter synthesizes its own internal reference signal based on the SIN and COS signal inputs. Therefore, the phase of the synthesized (internal) reference is determined by the signal input, resulting in reduced quadrature errors. The synthesized reference circuit also eliminates the 180 degree false error null hang up.

**FIGURE 4. ENABLE TIMING**

#### Notes:

- 1. Dimensions are in inches (millimeters).

- 2. Lead identification numbers are for reference only.

- Lead clusters shall be centered within ±0.01 of outline dimensions. Lead spacing dimensions apply only at seating plane.

- 4. Pin material meets solderability requirements to MIL-STD-202E, Method 208C.

- Case is electrically floating.

#### FIGURE 5. SDC-14610/15 MECHANICAL OUTLINE

#### **ORDERING INFORMATION**

Supplemental Process Requirements:

S = Pre-Cap Source Inspection

L = Pull Test

#### SDC-1461XX-XXXX

```

Q = Pull Test and Pre-Cap Inspection

K = One Lot Date Code

W = One Lot Date Code and PreCap Source

Y = One Lot Date Code and 100% Pull Test

Z = One Lot Date Code, PreCap Source and 100% Pull Test

Blank = None of the Above

Accuracy:

2 = 4 \text{ minutes} + 1 \text{ LSB}

4 = 2 minutes + 1 LSB (Not available with 14-bit units.)

5 = 1 minute + 1 LSB (Available with "S" option only.)

Process Requirements:

0 = Standard DDC Processing, no Burn-In (See TABLE 3)

1 = MIL-PRF-38534 Compliant

2 = B^*

3 = MIL-PRF-38534 Compliant with PIND Testing

4 = MIL-PRF-38534 Compliant with Solder Dip

5 = MIL-PRF-38534 Compliant with PIND Testing and Solder Dip

6 = B* with PIND Testing

7 = B* with Solder Dip

8 = B* with PIND Testing and Solder Dip

9 = Standard DDC Processing with Solder Dip, no Burn-In (See TABLE 3)

Temperature Grade/Data Requirements:

1 = -55^{\circ}C to +125^{\circ}C

2 = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}

3 = 0^{\circ}C \text{ to } +70^{\circ}C

4 = -55°C to +125°C with Variables Test Data

5 = -40°C to +85°C with Variables Test Data

8 = 0^{\circ}C to +70°C with Variables Test Data

Option:

Blank = Standard Velocity Output (VEL)

T = Built-In-Test Output (LOS and LOR), instead of VEL

S = Synthesized Reference with Built-In-Test Output instead of VEL (Only

available with input option 6 or 8)

Input Option:

0 = 11.8 V, Synchro, 14 bit, 400 Hz

1 = 11.8 V, Resolver, 14 bit, 400 Hz

2 = 90 V, Synchro, 14 bit, 400 Hz

3 = 2 V, Direct, 14 bit, 400 Hz

4 = 90 V, Synchro, 14 bit, 60 Hz

5 = 11.8 V, Synchro, 16 bit, 400 Hz

6 = 11.8 V, Resolver, 16 bit, 400 Hz (1kHz with "S" option)

7 = 90 V, Synchro, 16 bit, 400 Hz

8 = 2 V, Direct 16 bit, 400 Hz (2V, Differential 16 Bit, 1kHz for option "S" only)

9 = 90 V, Synchro, 16 bit, 60 Hz

```

<sup>\*</sup>Standard DDC Processing with burn-in and full temperature test—see TABLE 3 on next page.

| TABLE 3. STANDARD DDC PROCESSING |                            |              |  |  |  |

|----------------------------------|----------------------------|--------------|--|--|--|

| TEST                             | MIL-STD-883                |              |  |  |  |

| 1231                             | METHOD(S)                  | CONDITION(S) |  |  |  |

| INSPECTION                       | 2009, 2010, 2017, and 2032 | _            |  |  |  |

| SEAL                             | 1014                       | A and C      |  |  |  |

| TEMPERATURE CYCLE                | 1010                       | С            |  |  |  |

| CONSTANT ACCELERATION            | 2001                       | А            |  |  |  |

| BURN-IN                          | 1015, TABLE 1              | _            |  |  |  |

The information in this data sheet is believed to be accurate; however, no responsibility is assumed by Data Device Corporation for its use, and no license or rights are granted by implication or otherwise in connection therewith.

Specifications are subject to change without notice.

105 Wilbur Place, Bohemia, New York, U.S.A. 11716-2482

# For Technical Support - 1-800-DDC-5757 ext. 7382

Headquarters, N.Y., U.S.A. - Tel: (631) 567-5600 ext. 7382, Fax: (631) 567-7358 West Coast, U.S.A. - Tel: (714) 895-9777, Fax: (714) 895-4988 Southeast, U.S.A. - Tel: (703) 450-7900, Fax: (703) 450-6610 United Kingdom - Tel: +44-(0)1635-811140, Fax: +44-(0)1635-32264 Ireland - Tel: +353-21-341065, Fax: +353-21-341568 France - Tel: +33-(0)1-41-16-3424, Fax: +33-(0)1-41-16-3425 Germany - Tel: +49-(0)8141-349-087, Fax: +49-(0)8141-349-089 Japan - Tel: +81-(0)3-3814-7688, Fax: +81-(0)3-3814-7689 World Wide Web - http://www.ddc-web.com